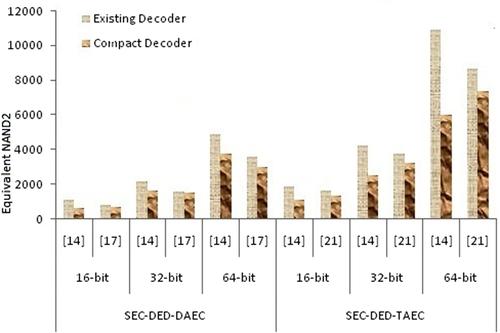

Multiple cell upsets (MCUs) caused by radiation is an important issue related to the reliability of embedded static random access memories (SRAMs). Multiple random and adjacent error correcting codes have been extensively employed for several years to protect stored data in SRAMs against MCUs. A compact and fast error correcting codec is desirable in most of these applications. In this study, simplified expressions for error location detection (ELD) block for single error correction-double error detection-double adjacent error correction (SEC-DED-DAEC) and single error correction-double error detection-triple adjacent error correction (SEC-DED-TAEC) decoders have been obtained by employing Karnaugh map. The conventional SEC-DED-DAEC and SEC-DED-TAEC decoders have been designed and implemented in both field-programmable gate array and ASIC platforms by considering these simplified ELD expressions. In FPGA platform, the proposed design for SEC-DED-DAEC and SEC-DED-TAEC decoders require 1.37–28.40% improvement in area and maximum 14.74% improvement in delay compared to existing designs. Whereas ASIC-based designs provide 2.20–26.81% reduction in area and 0.30–28.96% reduction in delay compared to existing related works. So the proposed design can be considered as an efficient alternative of traditional adjacent error correcting decoders in resource constraint applications.