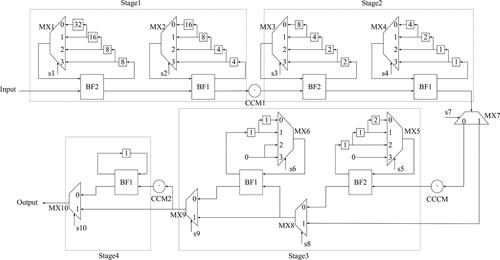

The authors present a novel 16/32/64/128-point single-path delay feedback pipeline fast Fourier transform (FFT) architecture targeting the multi-rate and multi-regional orthogonal frequency division multiplexing (MR-OFDM) physical layer of IEEE 802.15.4-g. The proposed FFT architecture employs a mixed-radix algorithm to significantly reduce the number of complex multipliers. It utilises a configurable complex constant multiplier structure instead of a fixed constant multiplier to efficiently conduct , , and twiddle factor multiplication. A hardware-sharing mechanism has also been formulated to reduce the memory space requirements of the proposed 16/32/64/128-point FFT computation scheme. The proposed design is implemented in Xilinx Virtex-5 and Altera's field-programmable gate array devices. For the computation of 128-point FFT, the proposed mixed-radix FFT architecture significantly reduces the hardware cost in comparison with existing FFT architecture. The proposed FFT architecture is also implemented by adopting the 90 nm complementary metal-oxide-semiconductor technology with a supply voltage of 1 V. Post-synthesis results reveal that the design is efficient in terms of gate count and power consumption, compared to earlier reported designs. The proposed variable-length FFT architecture gate count is 22.3K and consumes 3.832 mW, while the word-length is 12-bits and can be efficiently useful for the IEEE 802.15.4-g standard.