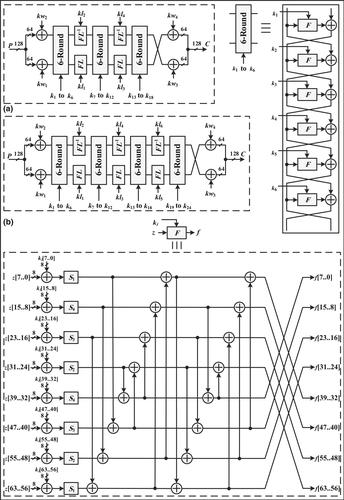

The advancements in wireless communication have created exponential growth in the Internet of Things (IoT) systems. Security and privacy of the IoT systems are critical challenges in many data-sensitive applications. Herein, high-throughput and flexible hardware implementations of the Camellia block cipher for IoT applications are presented. In the proposed structures, sub-blocks of the ciphers are implemented based on optimised circuits. The proposed structures for Camellia are designed and shared for implementing the encryption process and generating some intermediate key values in the two separate times. The most complex block in these ciphers is the substitution box (S-box). The S-boxes are implemented based on area-optimised logic circuits. The Camellia S-boxes consist of a field inversion over and two affine transformations over . The inversion operation is implemented over the composite field instead of an inversion over which is an important factor to reduce area consumption. A large number of gates, in the structure, have been implemented by 2-input NAND and 2-input NOR gates to reduce delay and area. Also, the flexible structure for Camellia that can do various configurations of this cipher to support variable key sizes 128, 192 and 256 bits was proposed. Implementation results of the proposed architectures in 180 nm CMOS technology for different key sizes are achieved. The results show improvements in terms of execution time, throughput and throughput/area compared to the other related works.